# Управление несколькими периферийными устройствами по линиям шин SPI/I<sup>2</sup>C

В статье сравниваются два распространенных последовательных цифровых интерфейса, используемых в большинстве аналоговых интегральных схем (ИС) — SPI (трехпроводной) и I²С (двухпроводной). Каждый из этих последовательных интерфейсов имеет свои преимущества и недостатки применительно к различным схемам, в зависимости от таких критериев, как необходимая скорость передачи данных, объем доступного пространства памяти и шумы. В настоящей статье обсуждаются различия между этими интерфейсами и приводятся примеры, подробно демонстрирующие возможности каждого из них.

Стив ЛОГАН

#### Введение

Хотя сигналы реального мира всегда будут аналоговыми, сегодня все в большем количестве аналоговых ИС коммуникация осуществляется через цифровые интерфейсы. Последовательные интерфейсы обеспечивают связь между ведущим устройством, предоставляющим последовательный тактовый сигнал, и ведомым или периферийным устройством. Порты SPI (трехпроводной) и I<sup>2</sup>C (двухпроводной), имеющиеся сегодня в большинстве микроконтроллеров, представляют собой популярные средства приема и передачи данных. Таким образом, микроконтроллеры ведут обмен данными по нескольким линиям шины для управления периферийными устройствами, такими как аналого-цифровые преобразователи (АЦП), цифро-аналоговые преобразователи (АЦП), батареи со встроенной логикой, расширители портов, ЭСППЗУ и датчики температуры. В отличие от параллельного интерфейса, в последовательном интерфейсе биты данных передаются один за другим — обычно по двум, трем или четырем линиям данных и синхронизации. Параллельные интерфейсы обеспечивают высокую скорость, зато последовательные требуют меньшего числа линий управления и данных.

### Основные сведения о последовательных интерфейсах

Последовательные интерфейсы выпускаются в трех разновидностях: трехпроводной, двухпроводной и однопроводной. Данная ста-

тья посвящена трех- и двухпроводным интерфейсам. В стандартах SPI, QSPI и MICROWIRE (или MICROWIRE PLUS) обмен данными осуществляется по трехпроводным интерфейсам. В стандартах ГС и SMBus обмен данными осуществляется по двухпроводным интерфейсам. Обоим типам последовательных интерфейсов свойственны как преимущества, так и недостатки (табл. 1).

#### Трехпроводной интерфейс

В трехпроводных интерфейсах используется линия выбора кристалла (CS или SS с активным низким уровнем), линия синхронизации (SCLK) и линия ввода данных или главная линия вывода (называется DIN или MOSI). Поскольку эти интерфейсы содержат также линию вывода данных или главную линию ввода (называется DOUT или MISO), их иногда называют четырехпроводными интерфейсами. Для простоты в данной статье трех- и четырехпроводные интерфейсы называются трехпроводными.

Трехпроводные интерфейсы работают на более высоких тактовых частотах и не требуют нагрузочных резисторов. Интерфейсы SPI/QSPI и MICROWIRE также обеспечивают полнодуплексный режим работы (данные могут одновременно передаваться и приниматься), и они более устойчивы к шумам. В трехпроводных интерфейсах синхронизация производится по фронту, а не по уровню.

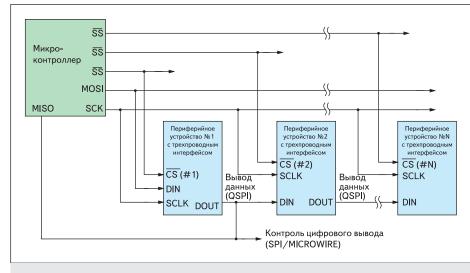

Основной недостаток трехпроводного интерфейса — необходимость в отдельной линии СS с активным низким уровнем для каждого ведомого устройства на шине, если только ведомые устройства не подключены по шлейфовой схеме, как показано на рис. 1. (Шлейфовая схема подключения более подробно обсуждается ниже.) Трехпроводной

**Рис. 1.** В трехпроводных интерфейсах используются линии ввода данных, вывода данных, синхронизации и выбора кристалла

интерфейс также не предусматривает подтверждения правильной передачи или приема данных. С точки зрения программирования трехпроводные интерфейсы проще и эффективнее двухпроводных при работе с одним ведущим и одним ведомым устройствами.

#### Двухпроводной интерфейс

В двухпроводных интерфейсах используется только линия данных (SDA или SMBDATA) и линия синхронизации (SCL или SMBCLK). Меньшее на одну или две количество линий — особенно актуальное преимущество для компактных устройств, таких как мобильные телефоны и волоконно-оптические системы. Двухпроводные интерфейсы также позволяют подключать множество ведомых устройств к одной шине без необходимости использования сигналов выбора кристалла. Это возможно благодаря тому, что каждое устройство имеет уникальный адрес. Двухпроводные интерфейсы также предусматривают передачу бита подтверждения после успешного чтения. Поскольку в двухпроводных интерфейсах имеется только одна линия данных, они способны работать только в полудуплексном режиме (в заданном такте возможны только передача или только прием данных, но не то и другое вместе). В двухпроводных интерфейсах синхронизация производится по уровню, что может создавать проблемы в условиях сильных шумов при неправильном определении бита данных.

Ведущее и ведомое устройства обмениваются данными по нескольким линиям шины последовательного интерфейса. В ходе цикла записи ведущее устройство использует собственные сигналы синхронизации и данных для передачи данных на ведущее устройство. В ходе цикла чтения ведомое устройство передает данные на ведущее.

## Конструктивные особенности интерфейсов SPI, QSPI, MICROWIRE

Интерфейсом SPI, который разработан компанией Motorola, оборудованы популярные процессоры и микроконтроллеры, такие как MAXQ2000 и MAXQ7654. Как уже отмечалось выше, схемы с интерфейсом SPI требуют двух линий управления (CS с активным низким уровнем и SCLK) и двух линий данных (DIN/SDI и DOUT/SDO). В стандартах SPI/OSPI компании Motorola линия данных DIN/SDI называется MOSI (master-out, slave-inвыход ведущего, вход ведомого), линия DOUT/SDO - MISO (master-in, slave-out вход ведущего, выход ведомого), а линия CS с активным низким уровнем — SS (slave-select – выбор ведомого). Для простоты и ясности в настоящей статье линии данных трехпроводного интерфейса будут рассматриваться с точки зрения ведомого устройства: DIN — это вход данных ведомого устройства, а DOUT — выход данных ведомого устройства. В этой ста-

Таблица 1. Преимущества и недостатки трех- и двухпроводных интерфейсов

| Интерфейс                                       | Преимущества                                                                                                           | Недостатки                                                                                                                                                                                                                            |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Трехпроводной:<br>SPI, QSPI<br>и MICROWIRE PLUS | Скорость.     Не требуются нагрузочные резисторы.     Полнодуплексный режим работы.     Устойчивость к шумам.          | Большее число подключений к линиям шины.     Для одновременного обмена данными более чем с одним ведомым устройством необходимы отдельные линии выбора кристалла.     Отсутствует подтверждение приема данных.                        |  |  |  |  |

| Двухпроводной:<br>I <sup>2</sup> C и SMBus      | Меньше подключений к линиям шины.     Множество угройств делят между собой одну шину.     Прием данных подтверждается. | Скорость:     для SMBus — не выше 100 кбит/с;     для I <sup>C</sup> C — не выше 3,4 Мбит/с.     Полудуплексный режим работы.     З. Для линий с открытым стоком требуются нагрузочные резисторы.     Сниженная устойчивость к шумам. |  |  |  |  |

тье линии трехпроводной шины обозначаются как CS с активным низким уровнем, SCLK, DIN и DOUT, поскольку именно такие названия используются в периферийных устройствах, выпускаемых компанией Maxim.

В большинстве интерфейсов SPI имеется два конфигурационных бита, определяющих момент выборки данных ведомым устройством — СРОL (полярность сигнала синхронизации) и СРНА (фаза сигнала синхронизации). Бит CPOL определяет состояние сигнала SCLK в режиме холостого хода (отсутствие переключения) — высокий уровень (CPOL = 1) или низкий уровень (CPOL = 0). Бит СРНА определяет, по какому фронту сигнала SCLK происходит сдвиг данных в том и другом направлении. Если CPOL = 0, то при CPHA = 0 данные будут сдвигаться на ведомое устройство по положительному фронту сигнала SCLK. При СРНА = 1 данные будут сдвигаться на ведомое устройство по отрицательному фронту сигнала SCLK. Два состояния битов CPOL и СРНА дают четыре возможных сочетания полярности и фазы сигнала синхронизации; каждое сочетание несовместимо с остальными тремя. Для успешного обмена данными между ведущим и ведомым устройствами на каждом из них должны быть установлены одинаковые значения СРОL и СРНА.

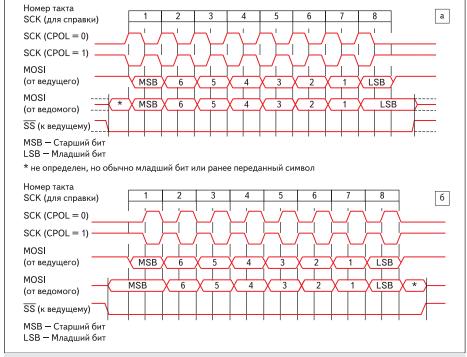

В простейшей форме интерфейс SPI перелает за олин прием восемь битов ланных (олин байт), хотя некоторые микроконтроллеры передают за один прием два или более байта. Например, микроконтроллеры MAXQ2000 и MAXQ7654 способны передавать за один прием 8 или 16 битов. При CPOL = 0 и CPHA = 0 переход от высокого уровня к низкому на линии CS с активным низким уровнем запускает передачу данных с ведущего устройства на ведомое. Сигнал на линии CS должен удерживаться на низком уровне, пока уровень сигнала SCLK будет меняться от низкого к высокому в течение восьми полных тактов. Данные DIN сдвигаются по положительному фронту сигнала SCLK. Байт данных загружается в ведомое устройство после того, как сигнал на линии CS с активным низким уровнем перейдет от низкого уровня к высокому. Данные будут доступны на линии DOUT ведомого устройства по отрицательному фронту сигнала SCLK на протяжении того же цикла из восьми битов. На рис. 2а приведена вре-

**Рис. 2.** а) Временная диаграмма работы трехпроводного интерфейса при СРНА = 1; 6) временная диаграмма работы трехпроводного интерфейса при СРНА = 0

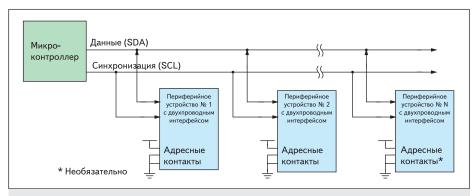

Рис. 3. В двухпроводных интерфейсах имеется линия ввода / вывода данных и линия синхронизации

менная диаграмма работы трехпроводного интерфейса SPI при СРНА = 1 и СРОL = 1. Потактовая передача данных на периферийное устройство производится по положительному фронту сигнала синхронизации, а с ведомого устройства — по отрицательному фронту. На рис. 26 приведена временная диаграмма работы трехпроводного интерфейса SPI при СРНА = 0 и СРОL = 1. Потактовая передача данных на периферийное устройство производится по отрицательному фронту сигнала синхронизации, а с ведомого устройства — по положительному фронту.

Линия шины CS с активным низким уровнем используется в качестве разрешающего сигнала для каждого ведомого устройства, поскольку каждой ИС на шине требуется собственная линия выбора кристалла. Если к одной шине подключено четыре ведомых устройства, для выбора соответствующего ведомого устройства необходимо четыре линии выбора кристалла. Если на линии CS с активным низким уровнем присутствует высокий (неактивный) уровень, ведомое устройство игнорирует фронты сигнала SCLK и удерживает линию DOUT в состоянии с высоким импелансом.

Некоторые периферийные устройства с трехпроводным интерфейсом можно программировать методом, который носит название шлейфового подключения. Вместо того чтобы подключать по одной линии CS с активным низким уровнем на каждое периферийное устройство, при шлейфовом подключении можно использовать одну линию CS с активным низким уровнем и линию SCLK для управления несколькими послеловательно соединенными периферийными устройствами. Для такого шлейфового подключения периферийных устройств в трехпроводном интерфейсе должна быть линия DOUT. Как показано на рис. 1, линия DOUT периферийного устройства  $\mathbb{N}$  1 служит линией DIN для периферийного устройства № 2 и т. д.

В стандарте SPI не нормирована максимальная скорость передачи данных. Вместо этого периферийные устройства сами задают максимальную скорость передачи данных, которая в большинстве случаев имеет порядок 1 Мбит/с. Микроконтроллеры способны работать в широком диапазоне скоростей передачи данных интерфейса SPI. Однако при прямой связи по шине SPI ведомое устройство не может принудить ведущее к снижению скорости передачи данных или подтвердить успешную передачу данных.

Стандарт QSPI почти идентичен SPI. Фактически периферийные устройства не могут отличить шину QSPI от шины SPI. В отличие от ведущих устройств с интерфейсом SPI, ведущие устройства с интерфейсом QSPI позволяют осуществлять передачу данных с программным выбором кристалла. Более того, ведущие устройства с интерфейсом QSPI могут передавать за один прием от 8 до 16 битов, а устройства с интерфейсом SPI обычно передают всего 8 битов. Устройства QSPI можно настроить для последовательной передачи до 16 слов данных (максимум 256 битов). Такой передачей целиком управляет интерфейс QSPI, и вмешательства микроконтроллера не требуется. Подобно SPI, стандарт QSPI не нормирует максимальную скорость передачи данных.

Более старый стандарт MICROWIRE, разработанный компанией National Semiconductor. весьма похож на SPI. Однако в MICROWIRE жестко заданы полярность и фаза сигнала синхронизации (CPOL = 0, CPHA = 0). Данные на линии DIN всегда сдвигаются на ведомое устройство по положительному фронту сигнала SCLK. Сдвиг данных с вывода DOUT происходит по отрицательному фронту сигнала SCLK. Подобно SPI, стандарт MICROWIRE не нормирует максимальную скорость передачи данных.

#### Интерфейс I<sup>2</sup>C

В отличие от трехпроводного полнодуплексного последовательного интерфейса, стандарт I2C, разработанный компанией Philips, предусматривает связь в полудуплексном режиме по одной линии данных (SDA) и одной линии управления (SCL). Стандарт I<sup>2</sup>С определяет простой двунаправленный интерфейс «ведуший-ведомый». В этой схеме микроконтроллер обозначает режим, в котором он будет работать — ведущий (режим передачи) или ведомый (режим приема). Каждое ведомое устройство имеет уникаль-

ный адрес, что позволяет ведущему устройству связываться с различными ведомыми устройствами по одной шине без использования сигналов выбора кристалла (рис. 3). Число ведомых устройств ограничено только максимально допустимой емкостью шины (400 пФ). В протоколе  $I^2$ С используются 7- или 10-разрядные адреса, хотя 7-разрядные адреса более распространены. При 7-разрядном протоколе к шине можно подключать до 127 различных периферийных устройств. SCL и SDA — это линии с открытым стоком, для надлежащей работы которых необходимо, чтобы в режиме холостого хода на них был установлен высокий уровень. При работе от источника питания напряжением 3 В к этим линиям следует подсоединить нагрузочный резистор сопротивлением 1 кОм или выше, а при работе от источника питания напряжением 5 В — 1,6 кОм

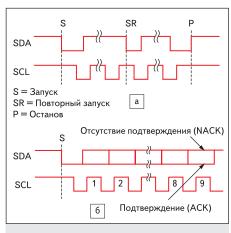

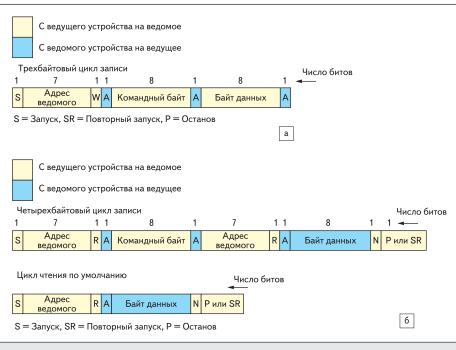

Обмен данными по интерфейсу I<sup>2</sup>C начинается с команды запуска, которая соответствует переходу линии SDA с высокого на низкий уровень при высоком уровне на линии SCL (рис. 4a). В двухпроводном интерфейсе для передачи данных между ведущим и ведомым устройствами используются команды запуска, повторного запуска и останова. За каждый такт SCL передается один бит данных; для передачи байта на ведомое устройство или с него необходимо передать как минимум девять битов. Цикл записи содержит восемь битов данных (рис. 46), за которыми следует сигнал подтверждения (АСК) или отсутствия подтверждения (NACK). Двухпроводной интерфейс устанавливает низкий уровень на линии SDA, когда передача данных подтверждается. Когда данные передаются по шине I<sup>2</sup>C, они сдвигаются на ведомое устройство по положительному фронту сигнала SCL и считываются по отрицательному фронту сигнала SCL. Данные на линии SDA должны быть устойчивы, пока тактовый импульс SCL имеет высокий уровень. Передача завершается при поступлении команды

Рис. 4. а) Условия запуска и останова в двухпроводном интерфейсе; б) биты подтверждения  $I^2C$

**Рис. 5.** а) Пример цикла записи  $I^2C$ ; б) примеры циклов чтения  $I^2C$

останова или повторной команды запуска; в этот момент линия SDA переходит с низкого уровня на высокий при высоком уровне на линии SCL. Как SDA, так и SCL сохраняют высокий уровень, когда шина свободна.

Цикл записи I<sup>2</sup>С начинается с команды запуска, за которой следует 7-разрядный адрес ведомого устройства и восьмой бит, указывающий на команду записи или чтения. Для передачи команды записи установите низкий уровень в восьмом бите, для передачи команды чтения — высокий. Ведущее устройство освобождает линию шины после восьмого такта. На девятом такте ведомое устройство удерживает низкий уровень на линии SDA, если оно подтверждает правильную передачу данных. Если ведомое устройство не подтверждает правильность выполнения команды записи, оно освобождает линию SDA (которая затем удерживается на высоком уровне нагрузочным резистором).

После этого ведущее устройство записывает 8-битный командный байт, за которым следует второй бит АСК/NАСК. Далее ведущее устройство записывает 8-битный байт данных, за которым следует третий бит АСК/NАСК. Конечный бит подтверждения байта данных завершает цикл чтения-записи, и выходы периферийного устройства обновляются. На рис. 5а показан пример цикла записи.

Цикл чтения I<sup>2</sup>С начинается с команды запуска, за которой следует адрес ведомого устройства с восьмым битом, обозначающим команду записи. После поступления бита АСК/NACK ведущее устройство записывает командный байт для доступа к новому регистру ведомого устройства. За вторым битом АСК/NACK ведущее устройство переписывает адрес ведомого устройства. Затем после

получения третьего бита АСК/NАСК ведомое устройство берет на себя управление шиной и записывает восемь битов данных за один прием (рис. 56). При чтении из того же регистра ведомого устройства, что и в предыдущих операциях чтения, ведущему устройству достаточно записать адрес ведомого устройства, прежде чем прочесть данные с этого ведомого устройства.

В двухпроводном интерфейсе передача данных происходит по восемь бит за один прием (рис. 5). Интерфейс I<sup>2</sup>С поддерживает медленные (до 100 кбит/с), быстрые (до 400 кбит/с) и высокоскоростные (до 3,4 Мбит/с) протоколы. Интерфейс I<sup>2</sup>С распознает сигналы высокого и низкого уровня по уровням напряжения КМОП-логики: напряжение низкого уровня составляет менее 0,3 от напряжения питания; сигнал высокого уровня составляет более 0,7 от напряжения питания.

#### Интерфейс SMBus

Стандарт SMBus был разработан корпорацией Intel для низкоскоростного обмена данными, и интерфейс SMBus похож на I<sup>2</sup>C. Подобно I<sup>2</sup>C, в SMBus используется двухпроводной интерфейс с линией данных (SMBDATA) и линией синхронизации (SMBCLK). Для линий SMBCLK и SMBDATA также требуются нагрузочные резисторы. При питании от источника напряжением 3 В следует использовать нагрузочный резистор сопротивлением 8,5 кОм и более, а при питании от источника напряжением 5 В 14 кОм и более. Шина SMBus питается от источника напряжением 3 или 5 В и распознает как сигнал высокого уровня напряжение выше 2,1 В, а как сигнал низкого уровня напряжение ниже 0,8 В.

Главное отличие между интерфейсами  $I^2C$  and SMBus заключается в величине таймаута, а также в минимальной и максимальной тактовой частоте. Шина I<sup>2</sup>C работоспособна на частотах до 0 Гц и не имеет таймаута по бездействию. В интерфейсе SMBus таймаут возможен. Тайм-аут происходит, когда ведомое устройство сбрасывает свой интерфейс после того, как сигнал синхронизации сохраняет низкий уровень в течение временного интервала, превышающего время ожидания (максимум 35 мс). Время ожидания интерфейса SMBus обусловливает минимальную тактовую частоту, равную 19 кГц. Для надлежащего обмена данными необходимо установить частоту сигнала SMBCLK в диапазоне от 10 до 100 кГц. Однако ведущее или ведомое устройство, подключенное к шине I2C, может удерживать сигнал синхронизации на низком уровне так долго, как это необходимо для обработки данных.

#### Примеры работы с периферийными устройствами

Микроконтроллеры часто ведут обмен данными с периферийными устройствами по последовательному интерфейсу. Используя трех- или двухпроводной интерфейс, микроконтроллер считывает и записывает данные во внутренние регистры периферийных устройств. Периферийные устройства далее устанавливают смещение различных аналоговых и цифровых выходов и управляют ими. Например, периферийные устройства программируют ток и напряжение зарядки батареи, управляют вращением вентилятора с помощью датчика температуры, устанавливают выходное напряжение ЦАП и напряжение смещения различных цепей.

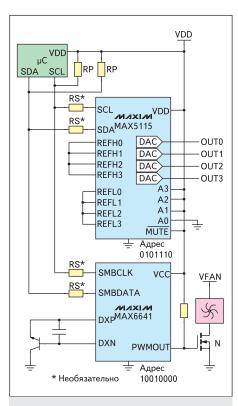

На рис. 6 показан микроконтроллер, обменивающийся данными с 8-разрядным ЦАП (МАХ5115) по двухпроводному интерфейсу. Поскольку у этого ЦАП имеются четыре адресных контакта, дающие 16 уникальных адресов ведомых устройств, возможно параллельное подключение до 16 ЦАП. Те же две линии шины можно было бы использовать для установки смещения контроллера вентилятора на базе датчика температуры с интерфейсом SMBus (МАХ6641), поскольку МАХ6641 имеет другой адрес как ведомое устройство. Этот контроллер управляет напряжением на затворе полевого МОП-транзистора для включения и выключения вентилятора.

В то время как трехпроводной интерфейс требует наличия отдельных линий выбора кристалла для обмена данными между микроконтроллером и множеством параллельно соединенных ИС, более простой двухпроводной интерфейс использует те же линии данных и синхронизации для связи с каждым устройством на шине. Можно соединить параллельно несколько ИС, установив для каждого периферийного устройства свой адрес как ведомого устройства.

Рис. 6. Поскольку данный микроконтроллер оборудован интерфейсом I<sup>2</sup>C, для обмена данными с различными периферийными устройствами, такими как параллельно соединенные ЦАП и датчик температуры, достаточно двух линий шины

Большинство периферийных устройств с интерфейсом I<sup>2</sup>C имеют адресные контакты, позволяющие присвоить собственный адрес ведомого устройства каждому из них. Ранее число адресов ведомого устройства, по которым могло идентифицироваться пе-

Таблица 2. Дешифрация 16 уникальных адресов по двум адресным линиям (AD2 и AD0) в МАХ7319

| Подключение контакта |                 | Адрес устройства |    |    |    |    |    |    |  |  |

|----------------------|-----------------|------------------|----|----|----|----|----|----|--|--|

| AD2                  | AD0             | A6               | A5 | Α4 | А3 | A2 | A1 | A0 |  |  |

| SCL                  | GND             | 1                | 1  | 0  | 0  | 0  | 0  | 0  |  |  |

| SCL                  | V <sub>cc</sub> | 1                | 1  | 0  | 0  | 0  | 0  | 1  |  |  |

| SCL                  | SCL             | 1                | 1  | 0  | 0  | 0  | 1  | 0  |  |  |

| SCL                  | SDA             | 1                | 1  | 0  | 0  | 0  | 1  | 1  |  |  |

| SDA                  | GND             | 1                | 1  | 0  | 0  | 1  | 0  | 0  |  |  |

| SDA                  | V <sub>cc</sub> | 1                | 1  | 0  | 0  | 1  | 0  | 1  |  |  |

| SDA                  | SCL             | 1                | 1  | 0  | 0  | 1  | 1  | 0  |  |  |

| SDA                  | SDA             | 1                | 1  | 0  | 0  | 1  | 1  | 1  |  |  |

| GND                  | GND             | 1                | 1  | 0  | 1  | 0  | 0  | 0  |  |  |

| GND                  | V <sub>cc</sub> | 1                | 1  | 0  | 1  | 0  | 0  | 1  |  |  |

| GND                  | SCL             | 1                | 1  | 0  | 1  | 0  | 1  | 0  |  |  |

| GND                  | SDA             | 1                | 1  | 0  | 1  | 0  | 1  | 1  |  |  |

| V <sub>CC</sub>      | GND             | 1                | 1  | 0  | 1  | 1  | 0  | 0  |  |  |

| V <sub>CC</sub>      | V <sub>cc</sub> | 1                | 1  | 0  | 1  | 1  | 0  | 1  |  |  |

| V <sub>cc</sub>      | SCL             | 1                | 1  | 0  | 1  | 1  | 1  | 0  |  |  |

| V <sub>CC</sub>      | SDA             | 1                | 1  | 0  | 1  | 1  | 1  | 1  |  |  |

риферийное устройство, было ограничено степенями двойки. Если, например, у периферийного устройства было два адресных контакта, он мог идентифицироваться на шине как ведомое устройство по четырем уникальным адресам.

В новых конструкциях обеспечивается возможность использовать больше адресов ведомых устройств при меньшем количестве адресных контактов. Например, расширитель портов ввода/вывода МАХ7319 можно запрограммировать на 16 уникальных адресов ведомого устройства, используя всего лишь два адресных контакта (AD2 и AD0). Эти контакты могут быть привязаны к «земле» (GND), напряжению питания (VCC), SDA или SCL. В таблице 2 показано 16 доступных адресов ведомого устройства. Хотя разряды А6, А5 и А4 должны быть установлены в значение 110, разряды А3—А0 могут программироваться че-

тырьмя различными состояниями контактов AD2 и AD0.

#### Перспективы на будущее

Сегодняшние трехпроводные интерфейсы служат для решения иных задач, чем двухпроводные интерфейсы, и каждый из типов интерфейсов обладает конкретными преимуществами. Маловероятно, что какой-либо из этих типов в будущем полностью вытеснит другой. Устройства с интерфейсом ГС прогрессируют быстрее за счет того, что начинают перенимать такие функции интерфейса SMBus, как сброс по тайм-ауту, которые могут быть отключены по необходимости. Новые адреса ведомых устройств с интерфейсом ГС имеют десятиразрядный формат вместо семиразрядного, обеспечивая пользователям еще большую гибкость.

Трех- и двухпроводные интерфейсы будут сосуществовать, но интерфейс I<sup>2</sup>C отвоюет, скорее всего, большую долю на рынке по мере того, как большее число микропроцессоров начнет поддерживать двухпроводные интерфейсы. Простота в использовании и меньшее количество линий шины, свойственные интерфейсу I<sup>2</sup>C, вероятно, поспособствуют более интенсивному росту его популярности в сравнении с SPI.

Для получения дополнительной информации обращайтесь к официальным дистрибьюторам компании Maxim в России: www.maxim-ic.ru/contact.

#### Литература

- 1. Указания по применению «Выбор последовательной шины» www.maxim-ic.com/an3967

- 2. Указания по применению «Последовательные цифровые сети данных» www.maxim-ic.com/an3438